The new integrated FIL workflow with HDL Coder and HDL Verifier from MathWorks enables customers to automatically generate test benches for hardware description language (HDL) verification, including VHSIC Hardware Description Language (VHDL) and Verilog, providing rapid prototyping and verification of designs.

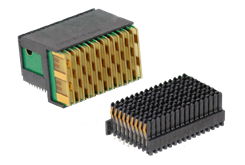

The collaboration with MathWorks enables customers to integrate MATLAB, a programming environment for algorithm development, data analysis, visualisation and numeric computation, and Simulink, a graphical environment for simulation and Model-Based Design, with Microsemi’s SmartFusion2 system-on-chip (SoC) FPGA and PolarFire FPGA development boards, which allows the stimulation of designs through FIL verification workflow using Microsemi’s development boards.

FIL verification workflow enables customers to analyze the results back in MATLAB and Simulink. “With the ever-increasing complexity in algorithm designs, it has become imperative for designers to quickly design and validate their algorithms on real hardware,” said Shakeel Peera, vice president FPGA marketing for Microsemi. “This integrated FPGA-in-the-loop workflow of Microsemi FPGA boards with MathWorks HDL Verifier will allow system engineers and algorithm developers to quickly prototype and implement their MATLAB and Simulink designs on Microsemi FPGA development boards through our Libero SoC Design Suite.”

Microsemi’s collaboration with MathWorks enables a unified workflow to verify designs comprehensively.It integrates Microsemi’s Libero SoC Design Suite—a comprehensive, easy to learn, easy to adopt development toolset for designing with Microsemi’s FPGAs and SoC FPGAs—with MATLAB and Simulink for design verification, and provides FIL verification with Microsemi FPGA boards.

This allows customers to catch bugs early in the design cycle, helping reduce time to market and enabling early verification.

“MATLAB and Simulink are widely used by engineers to develop algorithms targeting FPGAs,” said Paul Barnard, director of marketing for the Simulink product family at MathWorks. “Now that HDL Verifier supports FIL for Microsemi development kits, engineers can connect designs implemented on these FPGA boards directly to MATLAB and Simulink test benches, streamlining a crucial validation step in developing safety-critical avionics, space and other applications.”

Delivering the industry’s first FIL feature for Microsemi boards with MATLAB and Simulink, the collaboration provides HDL Verifier Support Package for Microsemi FPGA, a hardware support package for SmartFusion2 SoC FPGA and PolarFire FPGA development boards, and an integrated workflow from algorithms to implementation.

Leveraging HDL Verifer, enabled by Microsemi’s Accelerate Ecosystem, makes Microsemi’s FPGAs ideal for a wide variety of applications within the aerospace and defense, security, industrial and medical markets, including motor control and imaging, digital signal processing, communication systems, machine vision and imaging systems, control systems, military communications, and payload and radio processing.

The usage of FPGA verification significantly reduces timelines and development costs and has experienced considerable adoption in defense, automotive and industrial markets, leading to a booming $68 million for FPGA verification since September 2017 (as of March 2018), growing at a compound annual growth rate (CAGR) of nearly 8% through 2025 according to IndustryARC.

The market research firm also notes FPGA verification has an untapped potential market (total addressable market, or TAM) of $425 million with a tapped service addressable market (SAM) of $141 million.

Engineer News Network The ultimate online news and information resource for today’s engineer

Engineer News Network The ultimate online news and information resource for today’s engineer